Digital Cell Library Migration

Standard cell libraries form the core of digital circuits, allowing engineers to build circuits of enormous complexity.

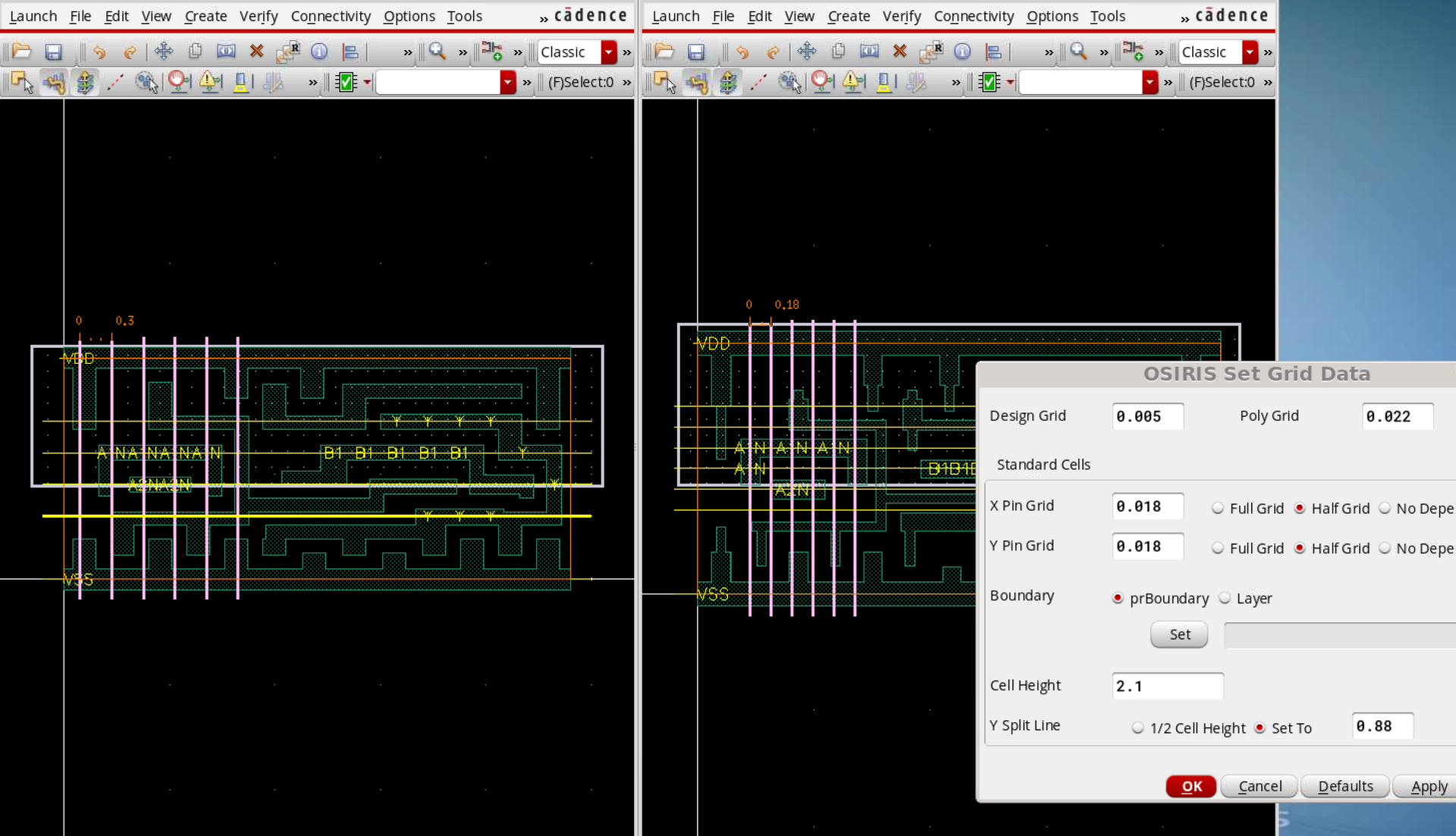

OSIRIS Standard cell tools deliver automation in library development that allows users to migrate libraries to new foundries, process nodes and routing grids in a matter of minutes. OSIRIS parses and generates control files for the Cadence VLM compaction engine and drives the library migration automatically to update hundreds of cells in a single pass.

Control File Generation

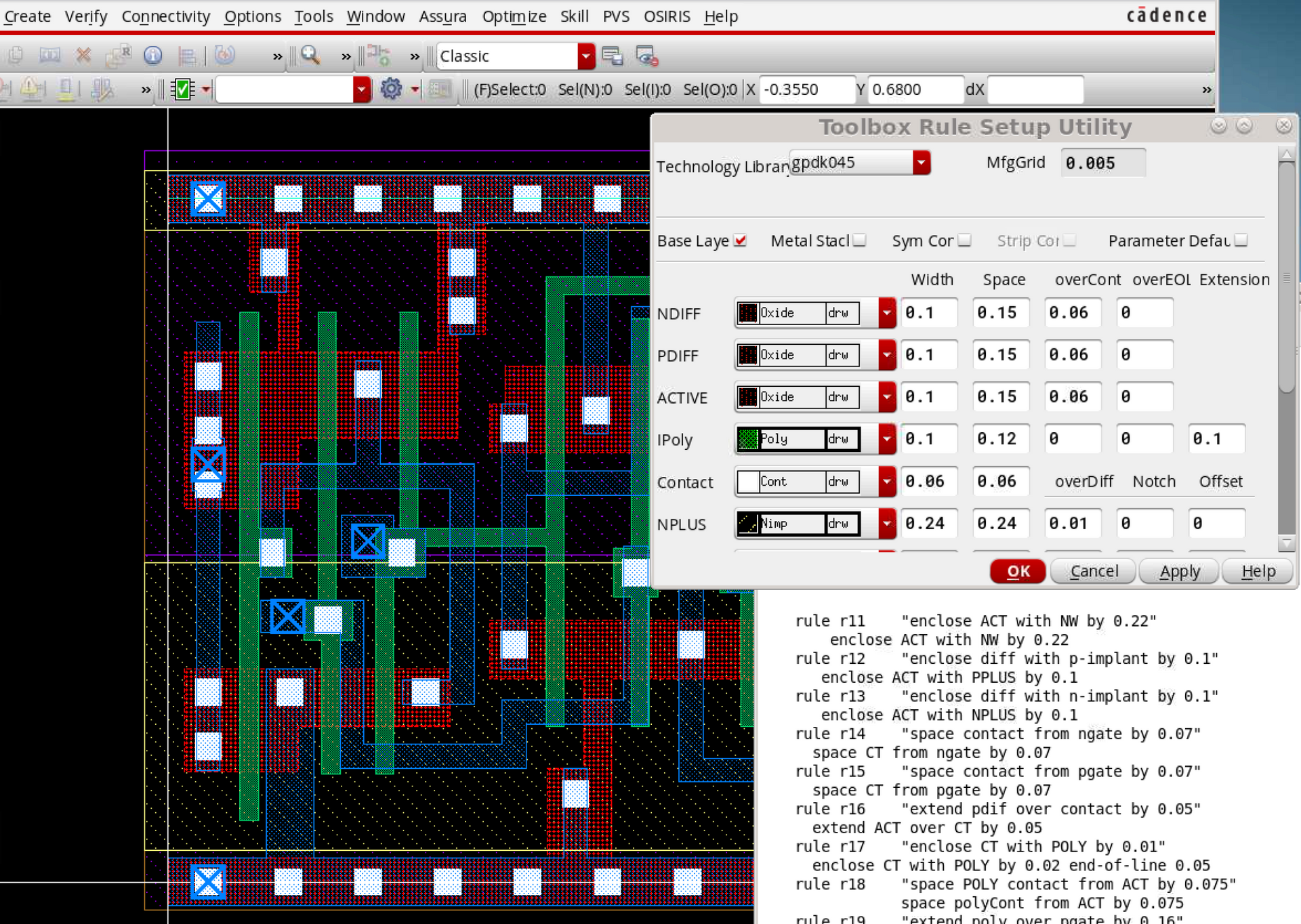

IN2FAB’s standard cell migration technology combines the interactive front end of the OSIRIS migration tools with the power of a compaction engine to deliver a migration system that can translate standard cell libraries in a matter of minutes. Once the new design rules are defined, each cell is updated to the new technology and every layout processed to enforce compliance with the new design rules.

OSIRIS retrieves the design rule information from the PDK technology file and compiles it into a control file for Cadence’s VLM tool. The file can be updated and edited to add extra features and functionality and then applied to the entire library in a single pass. Extra information such as cell height, power rails and well alignment is also included along with pin pitch to ensure routing compliance.

Control structures are automatically added to each cell prior to compaction to ensure that it meets the dimension and alignment rules for the placement tools. Pin grids can be adjusted to improve routing and deliver maximum circuit density through place & route.

OSIRIS Standard Cell delivers full control over the VLM compaction engine and relieves engineers from the burden of creating control files and alignment constraints. Outlines, well and implant alignment is set and gate sizes fixed as part of the migration flow to ensure cell alignment throughout the library.

Execution and Verification

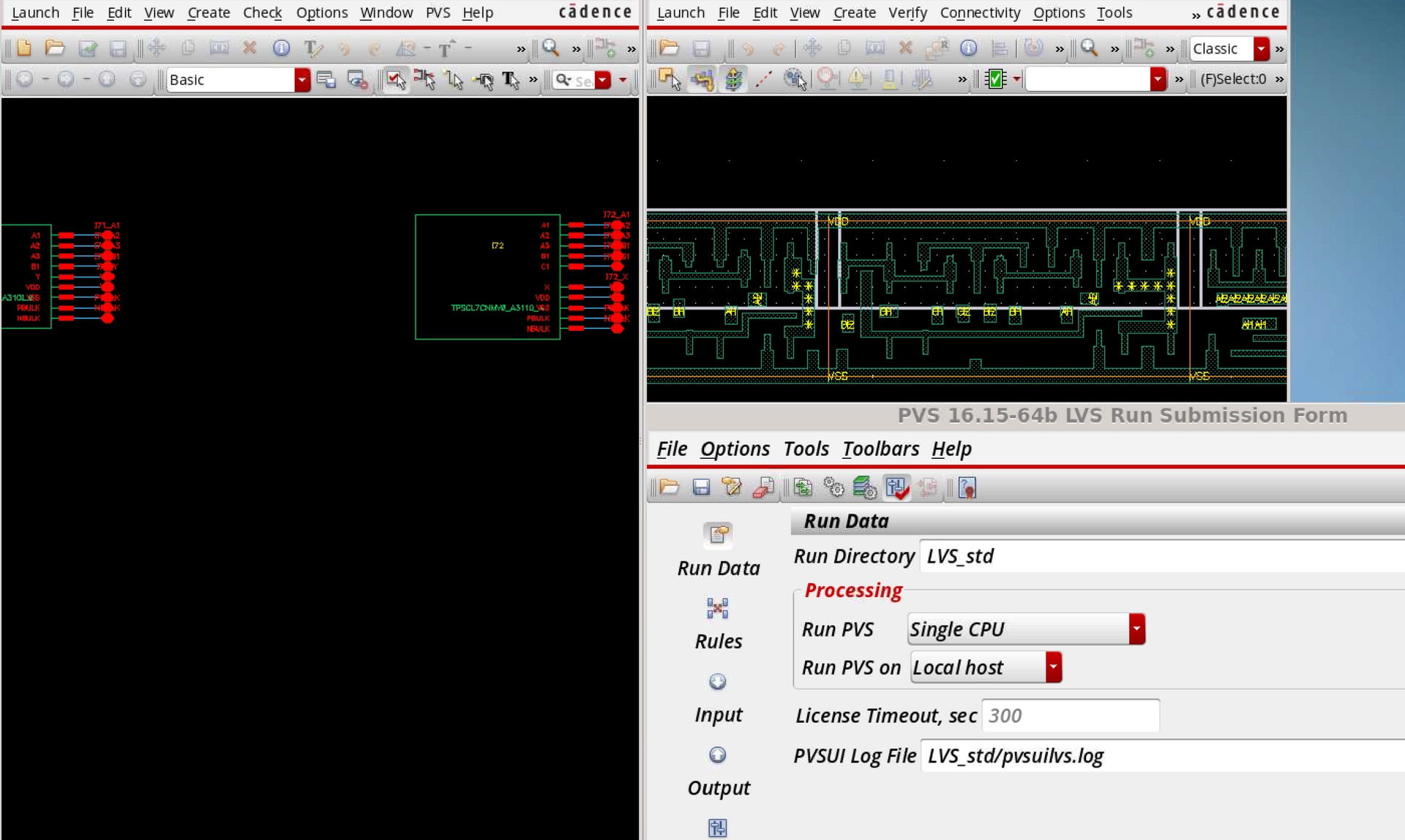

OSIRIS Standard Cell gives engineers complete control over the migration process, allowing users to experiment with different component sizes and routing pitches. Cells can be run individually or in groups as well as the entire library, with the compaction engine processing as many cells as required.

Standard cell migration can also be used to adjust silicon while maintaining the pin positions and routing metal. The footprint of the cell will remain identical to maintain the correct connections and enable changes to libraries that are already used in production.

Once the cells are processed, OSIRIS builds test structures to simplify DRC and LVS checks. Migrated views of schematic and layout are placed in to test structures to allow rapid processing through verification standard software. These include placement and reflection tests for each cell to ensure structures do not violate boundary rules during placement.

The entire process is completed within the Virtuoso editor to give layout engineers full control. Cells can be edited manually at any time to deliver the optimum results from the migration process.