回路図のマイグレーション

回路図のマイグレーションは、迅速かつ効率的にソフトウエア処理され、IPコアおよびフルチップのターゲットプロセスを評価するための不可欠なツールです。第一レベルのシミュレーションに向けた回路図マイグレーションは、新しいプロセスでの評価を可能にし、柔軟なIPプラットフォームのベースになります。

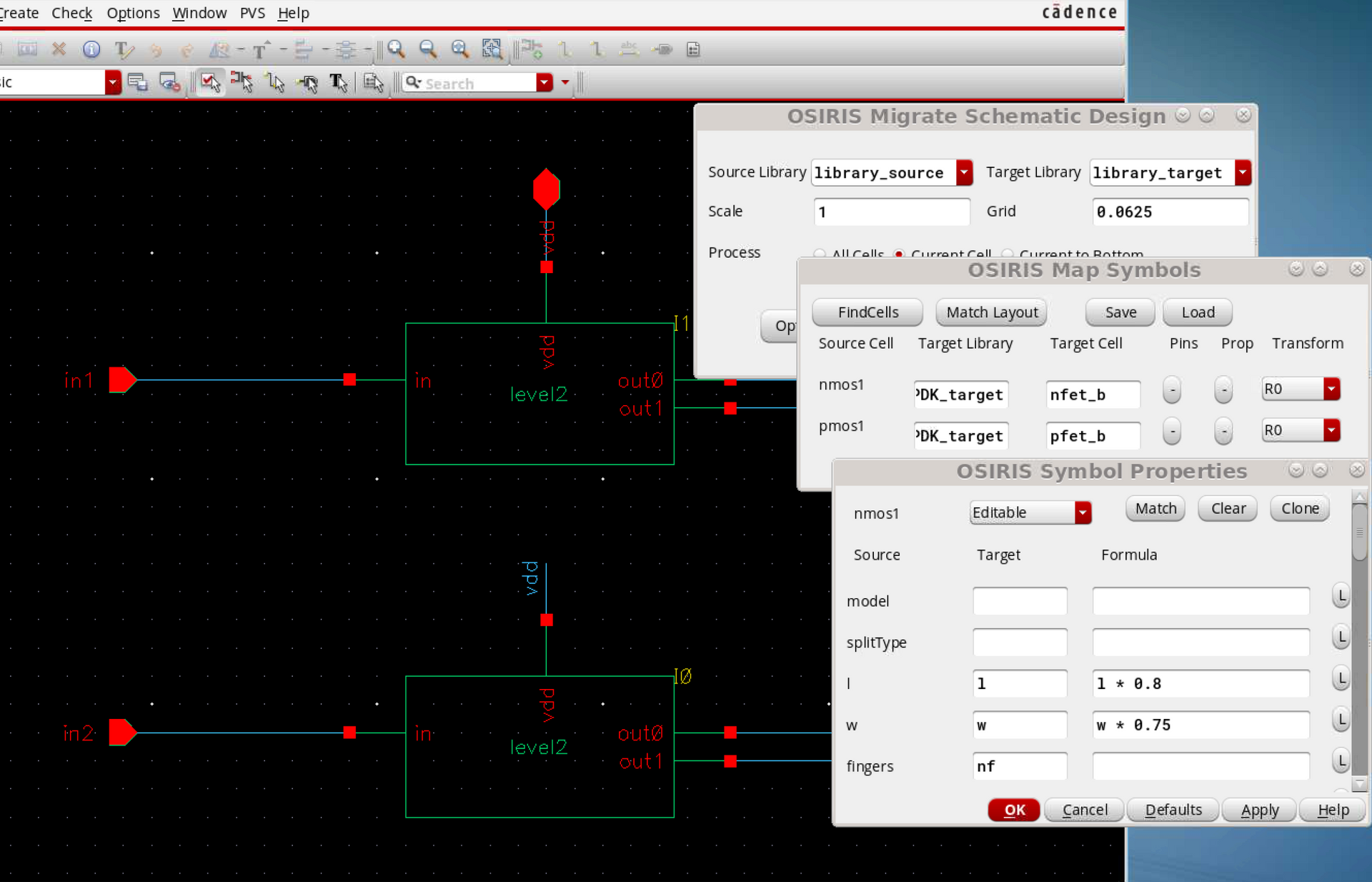

OSIRISの回路図マイグレーションは、最も強力で用途の広い回路図移行ツールを実現する多数の機能を備えています。レガシープロセスから最先端のナノメートルおよびFinFET設計に至るまで、OSIRISツールは個々の製造メーカーとカスタム ファウンドリのプロセス間で最も複雑な設計を移行することを容易にします。

ライブラリとコンポーネント

OSIRISのマッピング、配置、および再配線機能は、単純なコンポーネント スワッパーの機能をはるかに超え、数分で新しいファウンドリ のプロセスノードを全てのIP階層で変換できます。

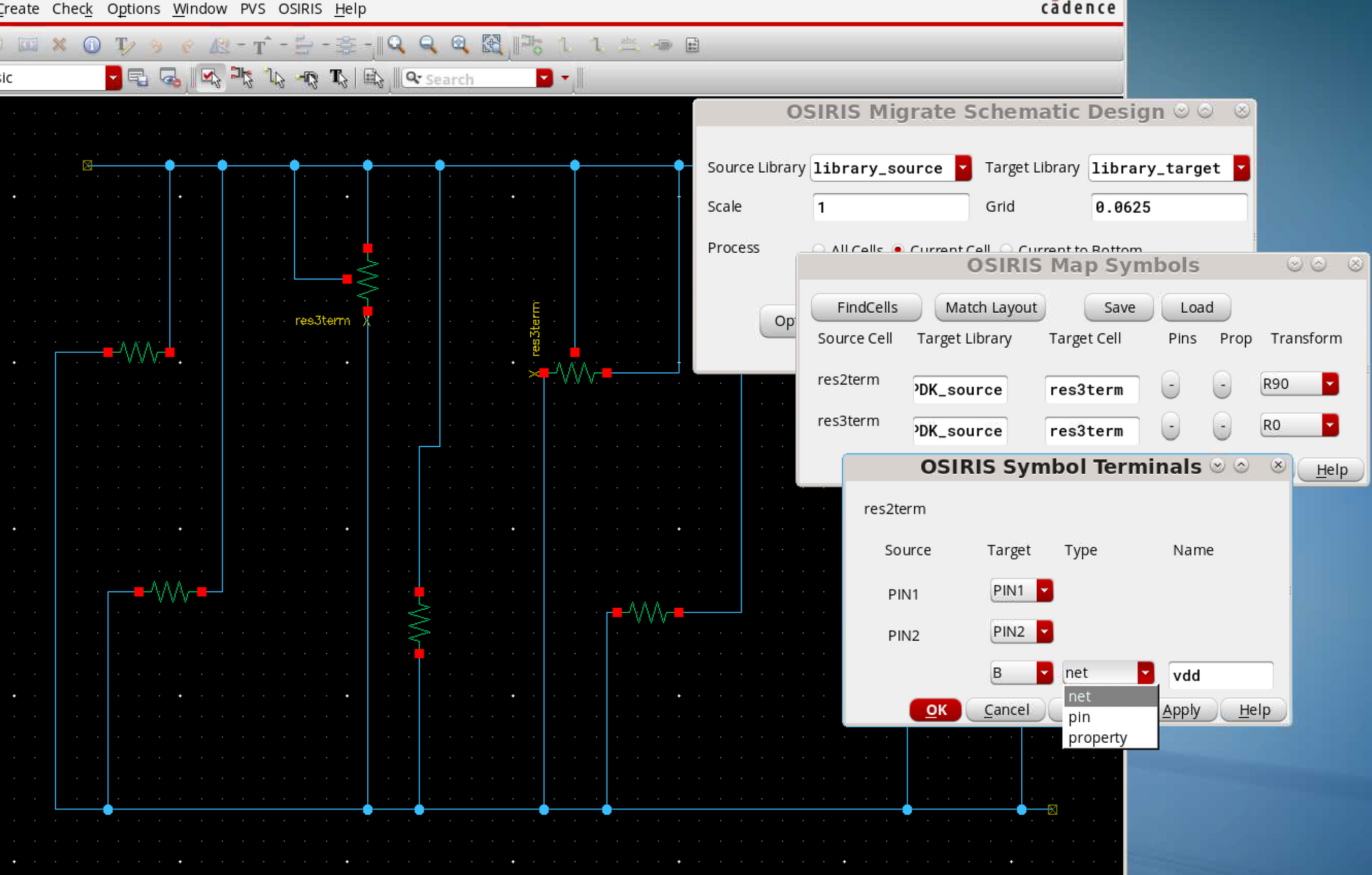

対話型GUIによる当ツールは、ソースデザインの回路シンボルを検出し、ピンとパラメーターのターゲットシンボルへのマッピングをエンジニアにガイド表示し、参照ライブラリ エレメントを新しいファウンドリの等価バージョンに置き換えることができます。

受け継がれるべきパラメータやネットセット プロパティなどの回路図データベースの高度な機能は完全に維持され、オリジナル設計の全機能を含む完全な回路図に変換されます。

OSIRISのAPIレベル拡張機能により、フローをカスタマイズして、最も複雑なマイグレーション要件の要求を満たすことができます。トランジスタの調整から複雑なパラメータ計算まで、最も困難なマッピングと変換の課題を解決し、IPを新しいファウンドリ、プロセスに迅速に移行します。

ピンとプロパティ

PDK間でピンとパラメータをマッピングする作業は、OSIRIS グラフィカル インターフェイスを介して大幅に簡素化されます。元のPDKと新しいPDKからの情報が認識され、明確なフォーマットでユーザーにウインドウ表示され、容易にマッピング及び変換が行うことができます。 これらの値の設定は、必要に応じて単純なスケーリングから複雑な関係性を必要するにもにも変更が可能です。

シンボルとピンの位置が異なる場合でも、確実な接続を維持・確保するため、マイグレーション処理の一環としてピンが自動的に再配線されます、また、新しいピンの位置の移動に起因する短絡が自動的に認識され解決されます。

インテリジェントなパラメーター割り当て、及びコールバックトリガー機能により、最も複雑なコンポーネントでも、シミュレーションまたはレイアウトのコンストレインに変換することが可能です。高度なコマンドセットは、複雑な要求やコンポーネントの変更にも対応し、ターゲットプロセスの難しいコンストレインを解決します。

比較とAPI 拡張

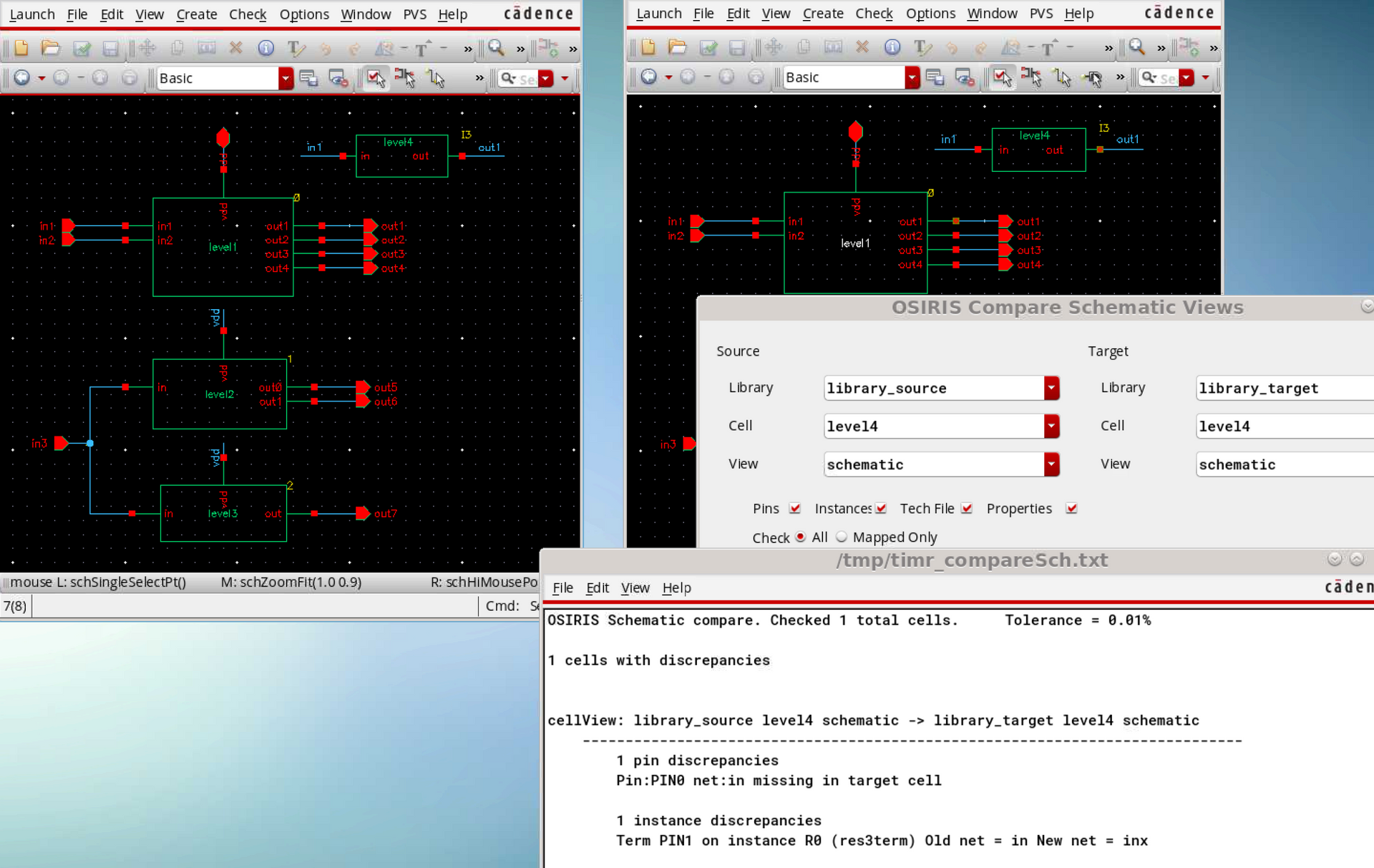

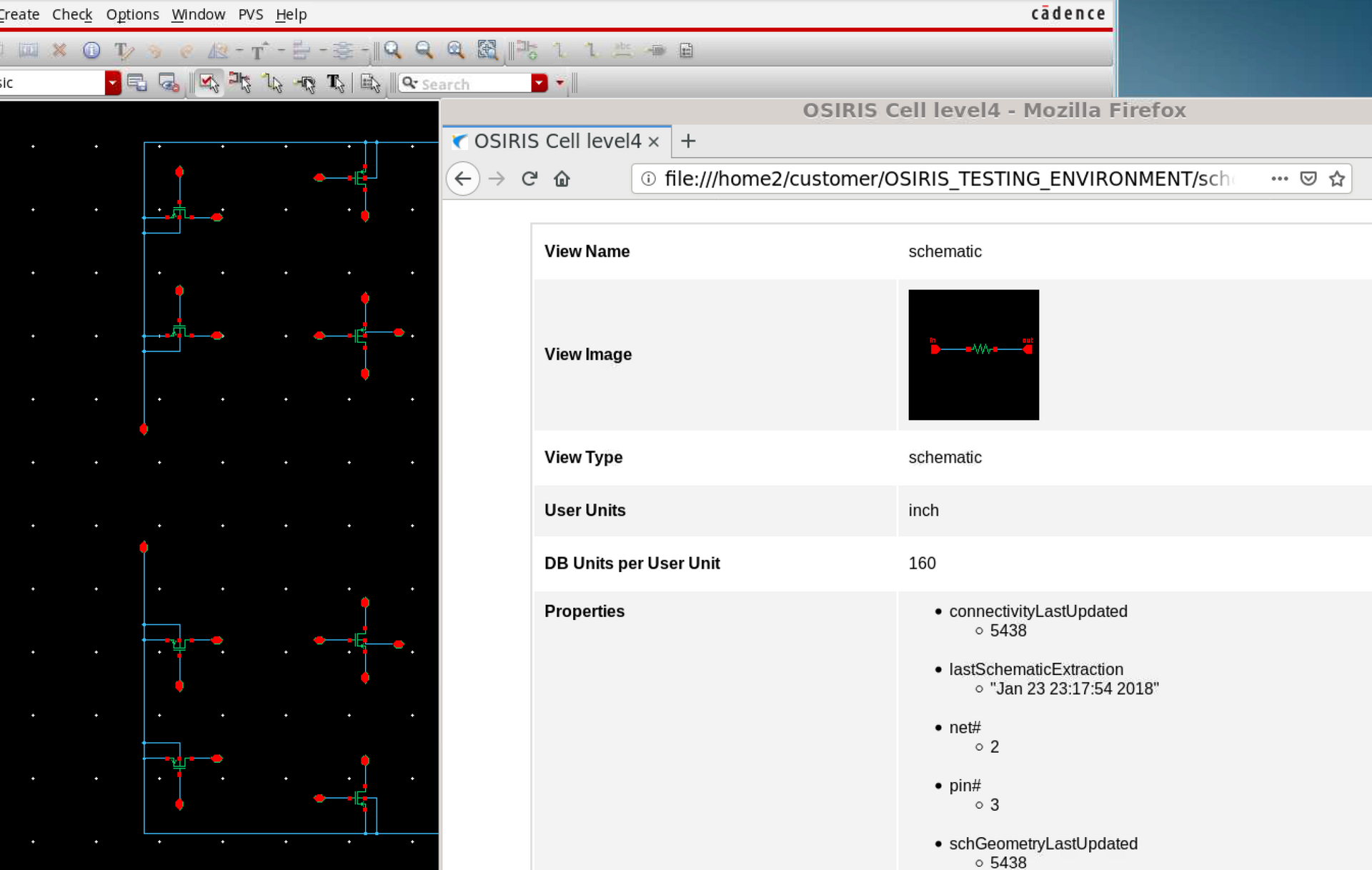

OSIRISは、ターゲット回路の配置、接続、およびパラメータをチェックしてオリジナルと一致することを確認する専用の変換比較ツールを備えています。回路階層は 1 回のパスでチェックされ、不一致を見つけた場合は、レビューのためにユーザーにフィードバックされます。

LVSツールとは異なり、回路図の比較では、コンポーネント名、パラメーターの種類、および値の違いが考慮され、古い回路と新しい回路の不一致が即座に認識・特定されます。最大/最小サイズの違反やコンポーネントの混雑などの問題は、簡単に識別できるように回路図エディタ内で報告され、強調表示されます。

OSIRISでは、Cadence Skill™プログラミング言語のAPI 拡張機能を呼び出して、複雑なパラメーターとプロパティのマッピングに対処することにより移行フローを強化します。ユーザーは、設計プロセスを合理化するための専用の OSIRIS マイグレーション機能とともに、全ての言語辞書を利用することができます。

APIレベルの拡張機能により、フローをカスタマイズして、最も複雑な移行要件の要求を満たすことができます。OSIRISは、トランジスタの調整から複雑なパラメータの計算まで、最も困難なマッピングと変換の課題を解決するために使用され、IPを新しいファウンドリ、プロセスに迅速なマイグレーションの実績があります。