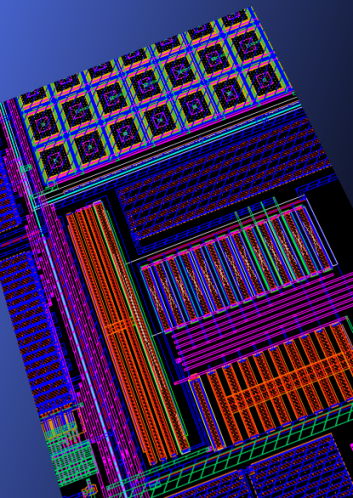

Analog circuits are built to withstand manufacturing variation. Designers account for process, parasitic, and environmental differences through symmetry, common-centroid placement, device matching, and conservative margins. These strategies create inherent resilience, which is precisely what makes direct layout migration so effective. Unlike migration through schematics, direct layout migration preserves placement, routing, matching structures, shielding, and non-active geometry, retaining the physical implementation of design intent that has already been proven in silicon. Much of what makes an analog circuit perform well is embedded in the layout itself, not captured by the schematic.

A key advantage of direct layout migration is that it preserves the layout hierarchy. By keeping the original hierarchical structure intact, very large circuits can be migrated efficiently without flattening or rebuilding them at the device level. This is a major differentiator compared to schematic-driven migration tools, which often focus on device sizing algorithms with little consideration for the existing layout. Those approaches require re-deriving the entire layout, re-optimizing placement, and rerouting connectivity, an effort that scales poorly for large analog blocks. In contrast, hierarchical layout preservation allows entire complex modules, such as serdes or wireless IP, to move between processes while retaining their proven connectivity, symmetry, and matching.