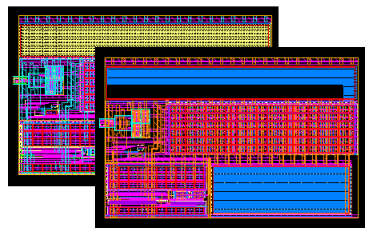

Global Foundries has invested heavily in new technologies including a range of Silicon on Insulator (SOI) processes for advanced SoCs. This process is ideal for devices that must combine high performance with extremely low power consumption but without the high cost of FinFET manufacturing.

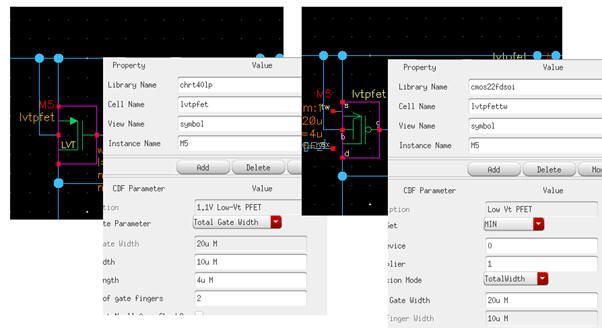

Migrating circuits to an SOI process presents extra challenges that are not found in bulk silicon technology. Devices can adjusted to take advantage of the benefits of body biasing and other factors like layer coloring, dummy shapes and layout dependent effects as well as complex changes in device construction and rules must also be addressed.

Migration from planar technology to SOI preserves the hierarchy and topology of the original circuit while adjusting the components to suit the new technology.