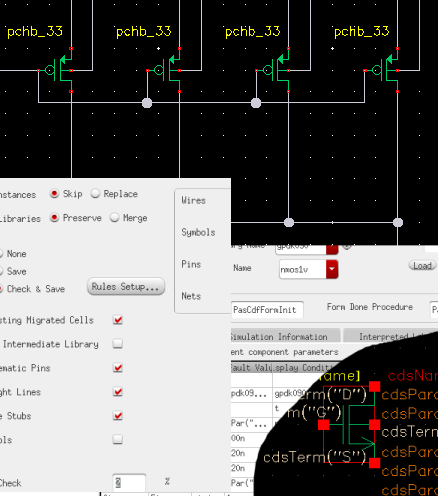

Migrating the schematics is reasonably straightforward as the cells will use a limited number of symbols, usually N and P transistors and antenna diodes. It may be possible to complete the task with an instance swapping script, although this may be complicated by restrictions in properties and callbacks. A fully featured schematic migrator can deal with those during the migration process, or they can be fixed by further enhancing the script.

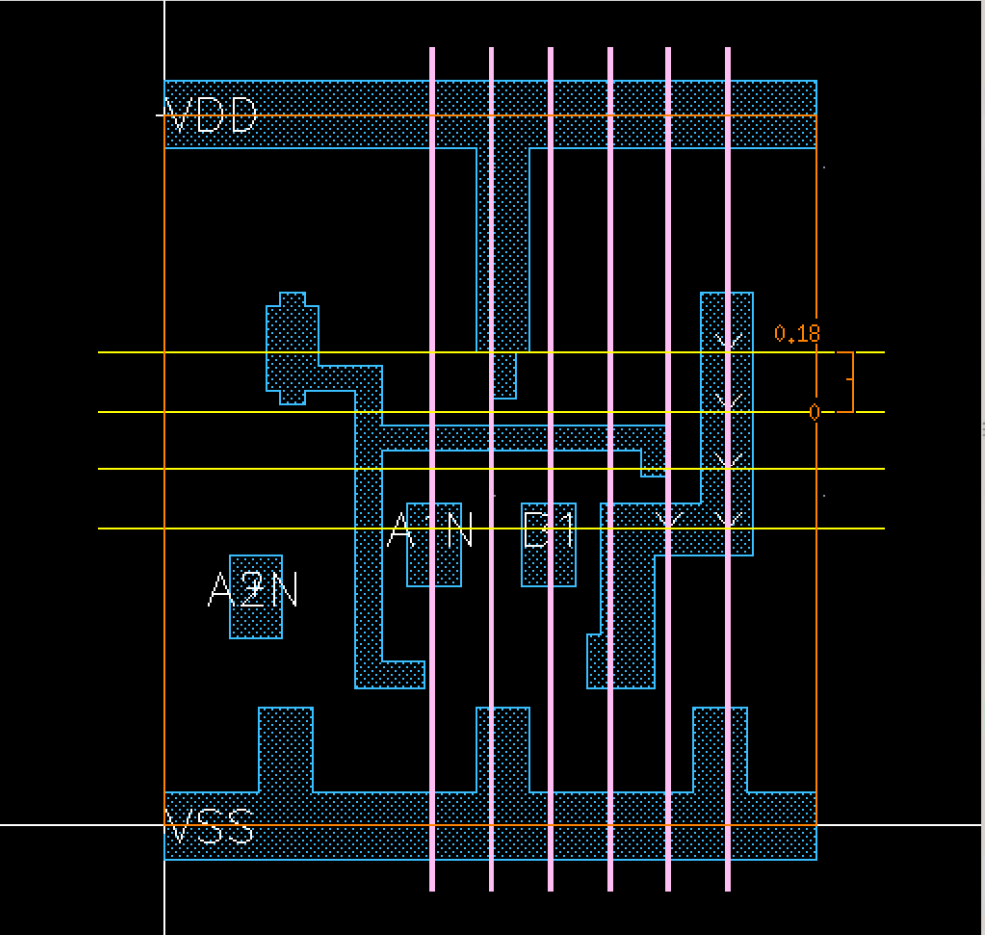

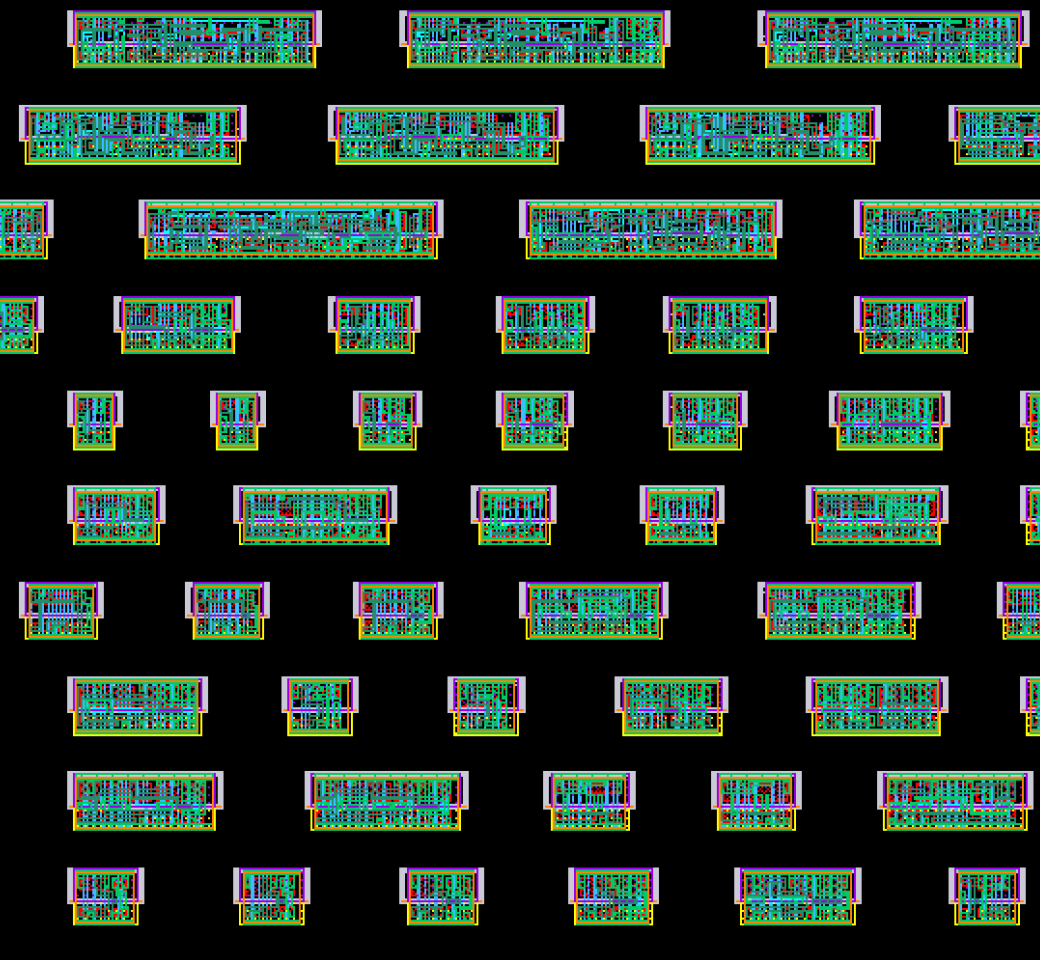

Engineers can adjust gate sizes to suit the new process. Gate lengths can be set to the target rules and widths adjusted to in proportion or by some other formula. More complicated adjustment may be needed for FinFET technology but this can all be programmed in to the migration flow.