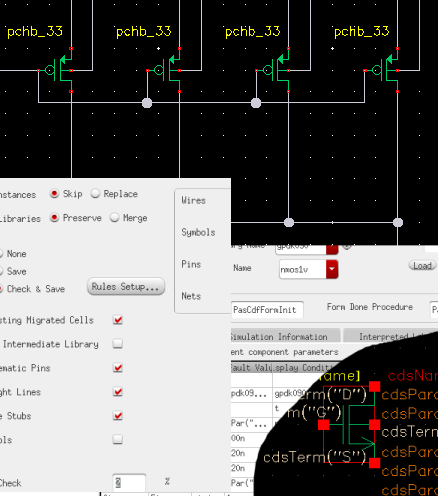

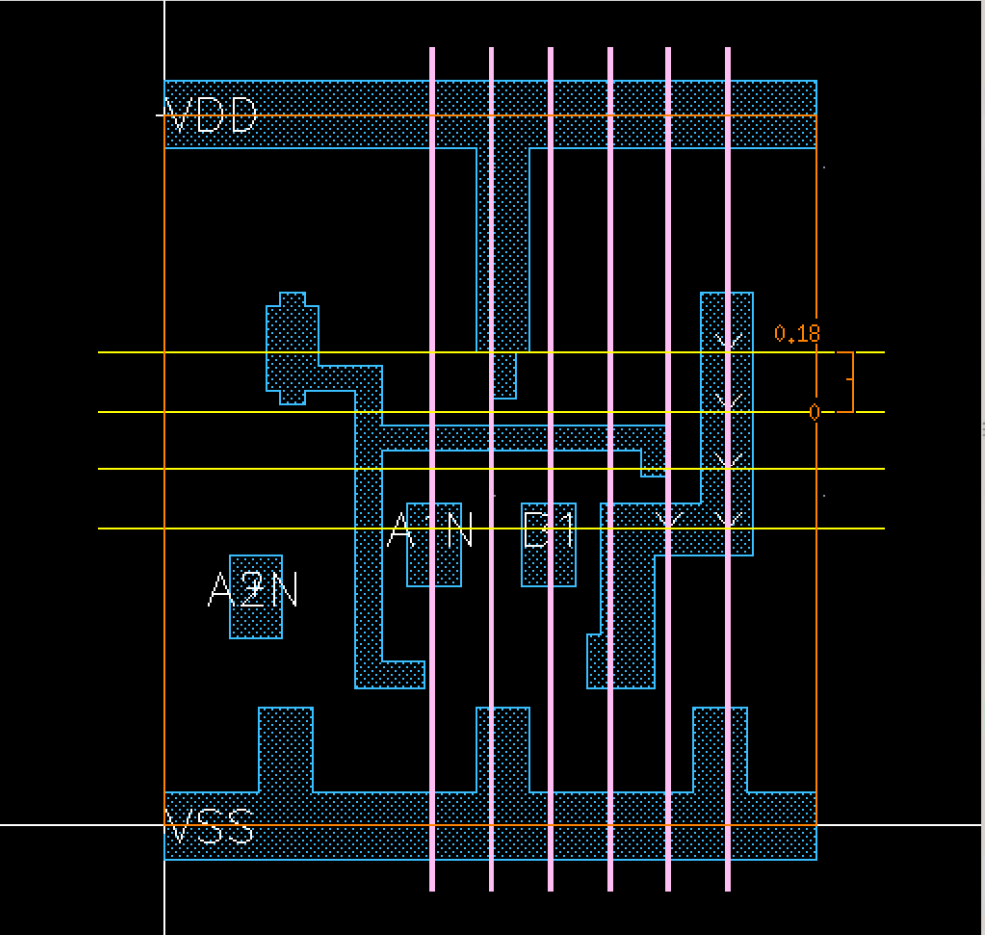

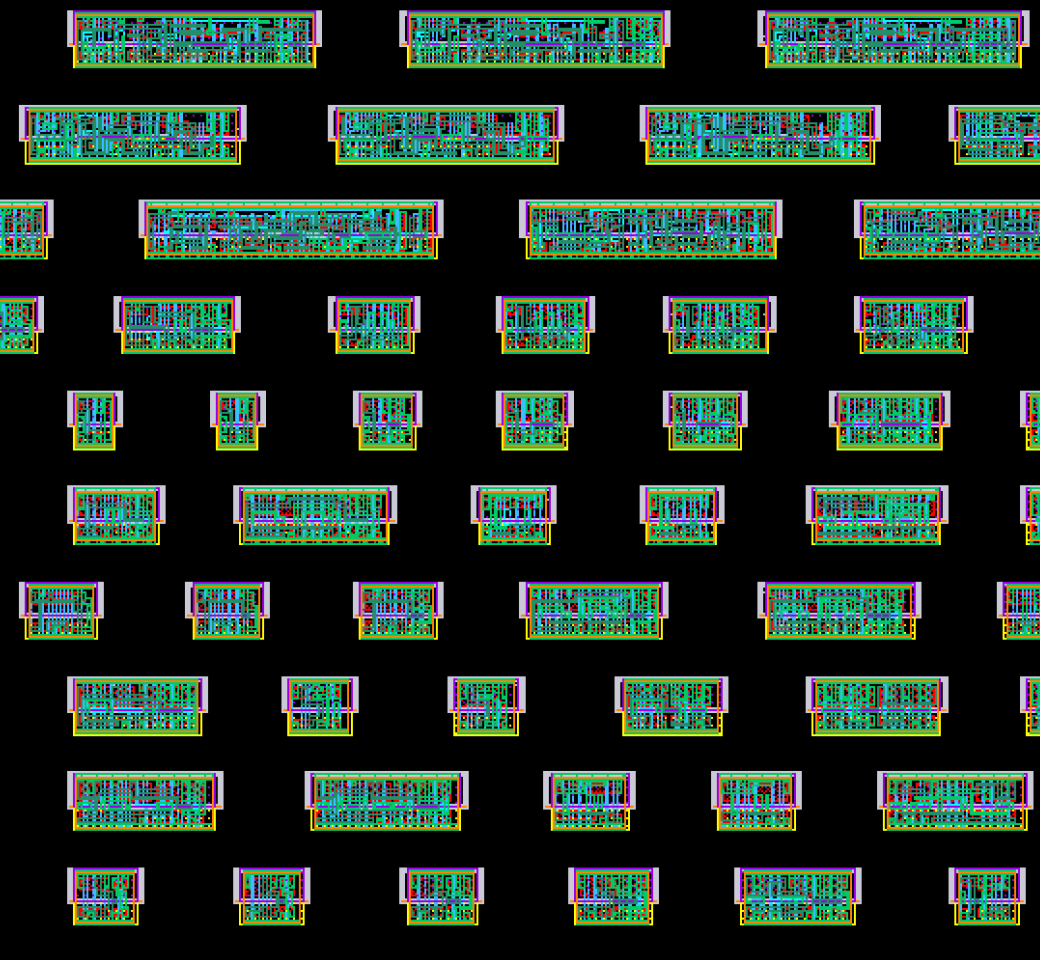

Standard Cells libraries form the core of digital circuits, allowing engineers to build IP of enormous complexity using a combination of logic generation front ends and place & route engines. These libraries usually contain hundreds of cells, ranging from simple logic gates to complex functions. Efficient use of space in standard cells can make an enormous difference to the size of a chip, with cells being replicated millions of times across the layout.

While commercial libraries are available, many companies develop their own to gain a technical advantage or simply avoid paying license fees. These become the bedrock of the design process and are used across a wide variety of circuits. However, this presents a problem when a company moves to a new technology as the library must be ported before any new products can be developed. This places a strain on the company’s library group who must make the standard cells available in the shortest possible time, which can lead to compromises in the cell design.